电子:从存力到封力:CoWoS研究框架

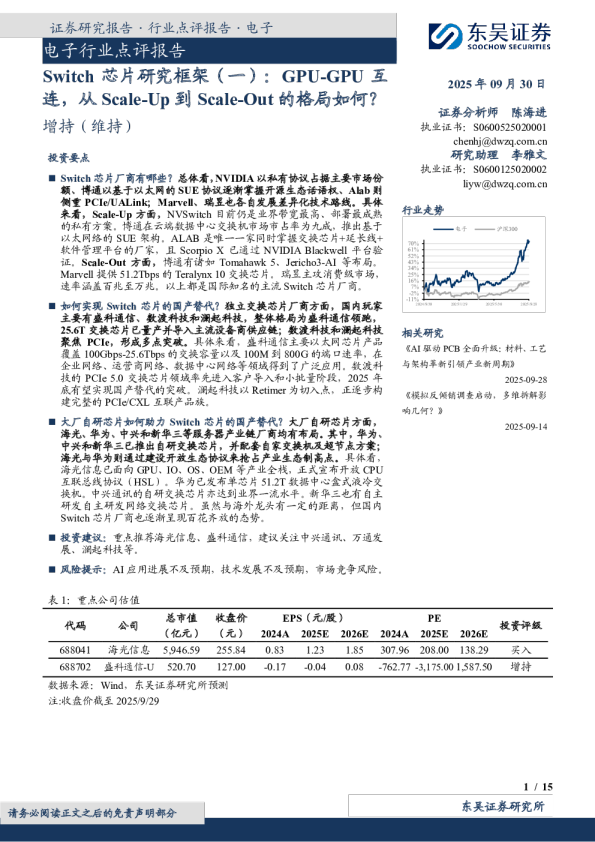

证券研究报告:电子|深度报告 2023年7月21日 行业投资评级 强于大市|维持 从存力到封力:CoWoS研究框架 8% 5% 2% -1% -4% -7% -10% -13% -16% -19% 电子沪深300 投资要点 行业相对指数表现(相对值) 行业基本情况收盘点位 3868.3 52周最高 4444.94 52周最低 3261.49 摩尔定律放缓,芯片特征尺寸已接近物理极限,先进封装成为提升芯片性能,延续摩尔定律的重要途径。先进封装是指处于前沿的封装形式和技术,通过优化连接、在同一个封装内集成不同材料、线宽的半导体集成电路和器件等方式,提升集成电路的连接密度和集成度。目前,带有倒装芯片(FC)结构的封装、晶圆级封装(WLP)、系统级封装(SiP)、2.5D封装、3D封装等均被认为属于先进封装范畴 先进封装增速高于整体封装,2.5D/3D封装增速居先进封装之首根据Yole,2021年,先进封装市场规模约375亿美元,占整体封装市场规模的44%,预计到2027年将提升至占比53%,约650亿美元,CAGR21-27为9.6%,高于整体封装市场规模CAGR21-276.3%。先进封装中的2.5D/3D封装多应用于(x)PU,ASIC,FPGA,3DNAND,HBM,CIS等, 受数据中心、高性能计算、自动驾驶等应用的驱动,2.5D/3D封装市 2022-072022-102022-122023-022023-052023-07 研究所 资料来源:聚源,中邮证券研究所 分析师:吴文吉 SAC登记编号:S1340523050004 近期研究报告 Email:wuwenji@cnpsec.com 《存力与AI共振》-2023.07.11 场收入规模CAGR21-27高达14%,在先进封装多个细分领域中位列第一先进封装处于晶圆制造与封测制程中的交叉区域,涉及IDM、晶 圆代工、封测厂商,市场格局较为集中,前6大厂商份额合计超过80%。全球主要的6家厂商,包括2家IDM厂商(英特尔、三星),一家代工厂商(台积电),以及全球排名前三的封测厂商(日月光、AmkorJCET),合计处理了超过80%的先进封装晶圆。 CoWoS(ChipOnWaferOnSubstrate)是台积电的一种2.5D先进封装技术,由CoW和oS组合而来,根据不同中介层(interposer分为CoWoS-S/R/L三种类型。其中CoWoS-S最为经典应用最广,采用硅作为中介层。CoWoS-R基于InFO技术,利用RDL中介层互连各chiplets。CoWoS-L结合了CoWoS-S和InFO技术的优点,使用内插器与LSI(本地硅互连)芯片进行芯片间互连,同时用于电源和信号传输的RDL层提供灵活集成。 超越摩尔(MorethanMoore,下文简称MtM)提速,制造设备为关键。采用全新结构的3D集成是推动半导体行业发展的重要技术,诸如存储器、逻辑器件、传感器和处理器等不同类型的器件和软件的复杂集成,以及新材料和先进的芯片堆叠技术,都需要基于3D集成技术。 晶圆级封装键合技术为实现3D集成的有力抓手。3D集成技术存在晶圆级对准精度、键合完整性、晶圆减薄与均匀性控制以及层内(层间)互联这4项挑战,随着摩尔定律逼近材料与器件的物理极限,源于微机电系统(MicroElectroMechanicalSystems,MEMS)制造技术的晶圆级封装键合技术逐渐进入集成电路制造领域,成为实现存储器、逻辑器件、射频器件等部件的三维堆叠同质/异质集成,进而提升器件性能和功能,降低系统功耗、尺寸与制造成本的重要技术途径。 其中熔融与混合键合使得芯片在性能上能够实现相当于更低工艺节点性能,同时扫除晶圆键合走向CMOS互联工艺的最大障碍。 光刻设备是超越摩尔变革的支柱,键合设备则推动先进封装的发展。就设备而言,晶圆级封装键合设备和光刻设备因超越摩尔(MtM提速愈发关键。MtM市场涵盖MEMS、CMOS图像传感器(CIS)、电源和射频(RF)以及先进封装(AP)等,MtM设备包括晶圆对晶圆(Wafer-to-Wafer,W2W)永久键合、光刻、临时键合和解键合设备。Yole测算2020年全球这三类MtM设备总规模为13.8亿美元,预计到2026年将超过24亿美元,CAGR2020-2026为10%,主要是由光刻设备驱动,其次为W2W永久键合。目前发达国家晶圆键合设备市场已比较成熟,国际一流晶圆键合设备厂商主要包括奥地利EVG公司与德国SUSSMicroTec公司等,而我国市场仍处成长阶段。随着3D集成技术的发展,在企业不断加大资金投入的基础上,晶圆键合系列设备市场将迎来井喷式发展,建议关注拓荆科技(混合键合),芯源微(临时键合和解键合)。 风险提示: 下游需求不及预期;行业景气度复苏不及预期;公司技术与产品迭代进展不及预期等。 建议关注: 晶圆代工:中芯国际 封装设备:拓荆科技,芯源微 封装材料:华海诚科,联瑞新材,德邦科技 封装:江波龙,深科技,长电科技,通富微电,晶方科技,甬矽电子,华天科技 目录 1后摩尔时代,先进封装成为提升芯片性能重要解法5 1.1摩尔定律放缓,先进封装日益成为提升芯片性能重要手段5 1.2先进封装份额占比提升,2.5D/3D封装增速领先先进封装6 1.3先进封装处于晶圆制造与封测的交叉区域7 2CoWoS:台积电的2.5D先进封装技术8 2.1CoWoS-S:最经典的CoWoS技术,以硅基板作为中介层9 2.2CoWoS-R:使用RDL替代硅作为中介层10 2.3CoWoS-L:使用小芯片和RDL作为中介层,融合CoWoS-S和InFO技术优点11 3超越摩尔(MtM)提速,制造设备为关键12 3.1光刻设备是超越摩尔的支柱,键合设备推动先进封装12 3.2MtM设备(W2W永久键合、光刻、临时键合和解键合设备)相关工艺与流程14 3.3MtM设备市场规模17 3.4MtM设备厂商18 图表目录 图表1:全球封装技术向先进封装迈进5 图表2:半导体封装技术演进路线图6 图表3:2020-2027年先进封装市场收入规模预测(单位:十亿美元)7 图表4:先进封装处于晶圆制造与封测制程中的交叉区域8 图表5:2021年先进封装按晶圆拆分市场份额(300MMEQWSPY)8 图表6:CoWoS结构:CoW+oS8 图表7:CoWoS-S结构9 图表8:CoWoS-S技术演进10 图表9:CoWoS-R结构10 图表10:CoWoS-R缓冲原理10 图表11:CoWoS-L结构11 图表12:MtM设备(W2W永久键合、光刻、临时键合和解键合设备)的技术路线图与相关应用13 图表13:晶圆键合及后续工艺流程14 图表14:晶圆键合工艺及典型器件15 图表15:混合键合优点之一:几乎消除了信号丢失16 图表16:SoIC和SoIC+的凸块密度路线图16 图表17:三维集成的主要晶圆键合技术示意图16 图表18:混合键合流程示意图16 图表19:2020-2026年MtM设备(W2W永久键合、光刻、临时键合和解键合设备)市场规模预测(十亿美元)17 图表20:全球MtM设备厂商19 图表21:2017年MtM设备市场竞争格局(百万美元)19 1后摩尔时代,先进封装成为提升芯片性能重要解法 1.1摩尔定律放缓,先进封装日益成为提升芯片性能重要手段 随着摩尔定律放缓,芯片特征尺寸接近物理极限,先进封装成为提升芯片性能,延续摩尔定律的重要手段。先进封装是指处于前沿的封装形式和技术,通过优化连接、在同一个封装内集成不同材料、线宽的半导体集成电路和器件等方式,提升集成电路的连接密度和集成度。当前全球芯片制程工艺已进入3-5nm区间,接近物理极限,先进制程工艺芯片的设计难度、工艺复杂度和开发成本大幅增加,摩尔定律逐渐失效,半导体行业进入“后摩尔时代”。集成电路前道制程工艺发展受限,但随着人工智能等新兴应用场景的快速发展,对于芯片性能的要求日益提高,越来越多集成电路企业转向后道封装工艺寻求先进技术方案,以确保产品性能的持续提升。以系统级封装(SiP)、倒装焊封装(FC)、扇出型集成电路封装 (Fan-Out)等为代表的先进封装技术应运而生,在“后摩尔时代”逐步发展为推动芯片性能提升的主要研发方向,也成为封装产业增长的主要驱动力。 图表1:全球封装技术向先进封装迈进 资料来源:艾森半导体招股说明书,中邮证券研究所 图表2:半导体封装技术演进路线图 资料来源:Yole,中邮证券研究所 1.2先进封装份额占比提升,2.5D/3D封装增速领先先进封装 AI带动先进封装需求。TrendForce报告指出,聊天机器人等生成式AI应用爆发式增长,带动2023年AI服务器开发大幅扩张。这种对高端AI服务器的依赖,需要使用高端AI芯片,这不仅将拉动2023~2024年HBM的需求,而且预计还将在2024年带动先进封装产能增长30~40%。 先进封装增速高于整体封装,2.5D/3D封装增速居先进封装之首。根据Yole,2021年,先进封装市场规模约375亿美元,占整体封装市场规模的44%,预计到 2027年将提升至占比53%,约650亿美元,CAGR21-27为9.6%,高于整体封装市场规模CAGR21-276.3%。先进封装中的2.5D/3D封装多应用于(x)PU,ASIC,FPGA,3DNAND,HBM,CIS等,受数据中心、高性能计算、自动驾驶等应用的驱动,2.5D/3D封装市场收入规模CAGR21-27高达14%,在先进封装多个细分领域中位列第一。 图表3:2020-2027年先进封装市场收入规模预测(单位:十亿美元) 资料来源:Yole,中邮证券研究所 1.3先进封装处于晶圆制造与封测的交叉区域 先进封装处于晶圆制造与封测制程中的交叉区域,涉及IDM、晶圆代工、封测厂商。先进封装要求在晶圆划片前融入封装工艺步骤,具体包括应用晶圆研磨薄化、重布线(RDL)、凸块制作(Bumping)及硅通孔(TSV)等工艺技术,涉及与晶圆制造相似的光刻、显影、刻蚀、剥离等工序步骤,从而使得晶圆制造与封测前后道制程中出现中道交叉区域,如图表4所示。 前后道大厂争先布局先进封装,竞争格局较为集中。后摩尔时代,先进制程成本快速提升,一些晶圆代工大厂发展重心正在从过去追求更先进纳米制程,转向封装技术的创新。诸如台积电、英特尔、三星、联电等芯片制造厂商纷纷跨足封装领域。先进封装竞争格局较为集中,全球主要的6家厂商,包括2家IDM厂商(英特尔、三星),一家代工厂商(台积电),以及全球排名前三的封测厂商(日月光、Amkor、JCET),共处理了超过80%的先进封装晶圆。 图表4:先进封装处于晶圆制造与封测制程中的交叉区域 图表5:2021年先进封装按晶圆拆分市场份额(300MMEQWSPY) 资料来源:艾森半导体招股说明书,中邮证券研究所资料来源:Yole,中邮证券研究所 2CoWoS:台积电的2.5D先进封装技术 CoWoS(ChipOnWaferOnSubstrate)是台积电的一种2.5D先进封装技术,由CoW和oS组合而来:先将芯片通过ChiponWafer(CoW)的封装制程连接至硅晶圆,再把CoW芯片与基板(Substrate)连接,整合成CoWoS。核心是将不同的芯片堆叠在同一片硅中介层实现多颗芯片互联。在硅中介层中,台积电使用微凸块(μBmps)、硅通孔(TSV)等技术,代替了传统引线键合用于裸片间连接,大大提高了互联密度以及数据传输带宽。CoWoS技术能够提高系统性能、降低功耗、缩小封装尺寸,也为台积电在后续的封装技术保持领先奠定了基础。 图表6:CoWoS结构:CoW+oS 资料来源:Wikichip,中邮证券研究所 根据采用的不同的中介层(interposer),台积电把CoWoS封装技术分为三种类型——CoWoS-S(SiliconInterposer)、CoWoS-R(RDLInterposer)